0.71

Sep. 23, 09

TL

| Rev | Date        | Initial | Note                     |

|-----|-------------|---------|--------------------------|

| 0.7 | Sep. 18, 09 | TL      | Initial internal release |

Added descriptions of NC balls to Ballout and Ball Lists

# Table of Contents

| Revision History                                       |             |     |

|--------------------------------------------------------|-------------|-----|

| Table of Contents                                      |             |     |

| List of Figures                                        |             |     |

| List of Tables                                         |             | V   |

| Product Features                                       |             |     |

| WM8505 System Overview                                 |             | 5   |

| Ballout: 479-ball PBGA Package (19 x 19 mm with 0.8 mm | ball pitch) | 7   |

| Ball Lists: WM8505 479-ball PBGA Package               |             | 9   |

| Signal Ball List: WM8505 479-ball PBGA Package         |             |     |

| Signal Ball List: WM8505 479-ball PBGA Package         |             |     |

| Signal Ball List: WM8505 479-ball PBGA Package         |             |     |

| Signal Ball List: WM8505 479-ball PBGA Package         |             |     |

| Signal Ball List: WM8505 Power and Ground Ball         | l ist       | 13  |

| Signal Description                                     |             |     |

| DRAM Interface                                         |             |     |

| Serial Flash Memory Controller Interface               |             |     |

| Ethernet MAC Interface                                 |             |     |

| USB 2.0 Host and Device Interface                      |             |     |

| PS/2 Keyboard Mouse Interface                          |             |     |

| NAND Flash Interface                                   |             |     |

| NOR Flash/Generic uP Interface                         |             | 10  |

|                                                        |             |     |

| SD/MMC Interface                                       |             |     |

| DVO Interface                                          |             |     |

| Video Input Device (CCIR601/656) Interface             |             |     |

| VGA Output Interface                                   |             | 1/  |

| Keypad Interface                                       |             | 18  |

| Real Time Clock Interface                              |             | 18  |

| Power Management Interface                             |             | 18  |

| UART Interface                                         |             |     |

| Pulse Width Modulation Interface                       |             |     |

| SPI Interface                                          |             | 20  |

| I <sup>2</sup> C Interface                             |             |     |

| AC97 Interface                                         |             | 20  |

| Audio I <sup>2</sup> S Interface                       |             |     |

| ARM JTAG Interface                                     |             |     |

| Clock Support Interface                                |             | 21  |

| Miscellaneous Interface                                |             | 21  |

| General Purpose Input/Output Interface                 |             |     |

| Power and Ground                                       |             | 25  |

| Register Overview                                      |             |     |

| Memory Map                                             |             |     |

| Attribute Definitions                                  |             | 28  |

| Register Descriptions                                  |             | 29  |

| GPIO Control Registers                                 |             | 29  |

| Power Management Control Registers                     |             | 66  |

| Interrupt Controller Registers                         |             |     |

| UART Control Registers                                 |             | 109 |

| PWM Control Registers                                  |             |     |

| SPI Control Registers                                  |             |     |

| Keypad Controller Registers                            |             |     |

| CIR Receiver Control Registers                         |             |     |

| I <sup>2</sup> C Control Registers                     |             |     |

| AC97 Control Registers                                 |             |     |

| I <sup>2</sup> S Control Registers                     |             |     |

| Functional Descriptions                                |             |     |

| Power Management                                       |             |     |

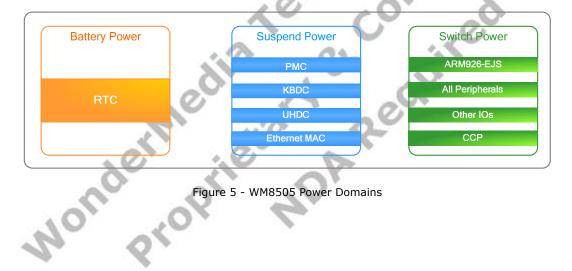

| Power Domains                                          |             |     |

|                                                        |             |     |

| Power Sequence                                         |             |     |

| Power Sequence                                         |             |     |

| Strapping Options                                      |             |     |

| Clock Architecture                                     |             |     |

| 27 MHz Clock Source                                    |             |     |

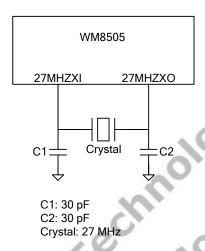

| Internal Clock Generation                              |             | 186 |

| RTC Clock Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 187                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 188                      |

| DMA Controller Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

| DMA Bus Interface Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| Basic DMA Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

| DMA Channel Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |

| Possible System DMA Transfer Sources and Destinations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| Data Sizes and Data Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Burst Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 191                      |

| Transfer Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 192                      |

| Error Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 192                      |

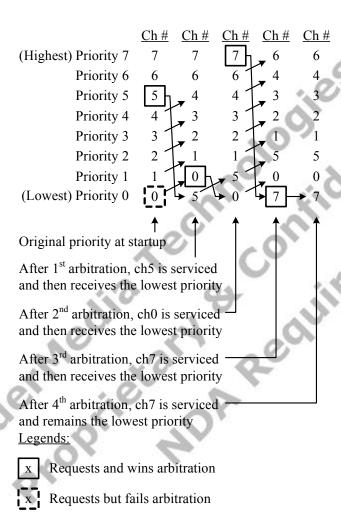

| DMA Request Priority Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

| Software DMA Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| Interrupt Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

| Dual Buffer Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| LCD Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| LCD Controller DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| Frame Buffer Data Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |

| Frame Buffer Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 196                      |

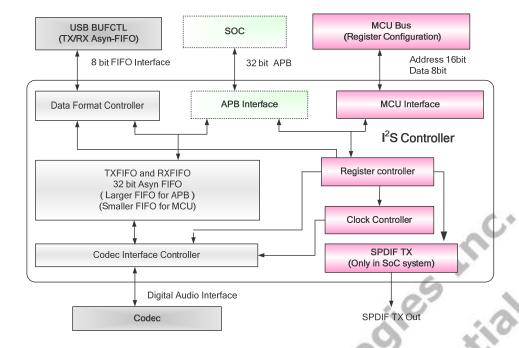

| Audio I <sup>2</sup> S Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 197                      |

| General Purpose Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

| Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| Interrupt Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| External Interrupt Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

| Interrupt Request Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 199                      |

| UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 201                      |

| UART Clock & Baud Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 201                      |

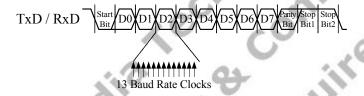

| Serial Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 201                      |

| Break Signal Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 201                      |

| Baud Rate Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 201                      |

| IrDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 202                      |

| FIFO Access & DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 202                      |

| The UART module can function in two modes, Register mode or FIFO mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| Non-FIFO Operation Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

| FIFO w/o DMA Operation Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 202                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

| FIFO w/ DMA Operation Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| FIFO Threshold & DMA Burst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| DMA Request and Threshold Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |

| Trailing Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 204                      |

| Overflow / Underflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 205                      |

| Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 205                      |

| OS Timers and Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 205                      |

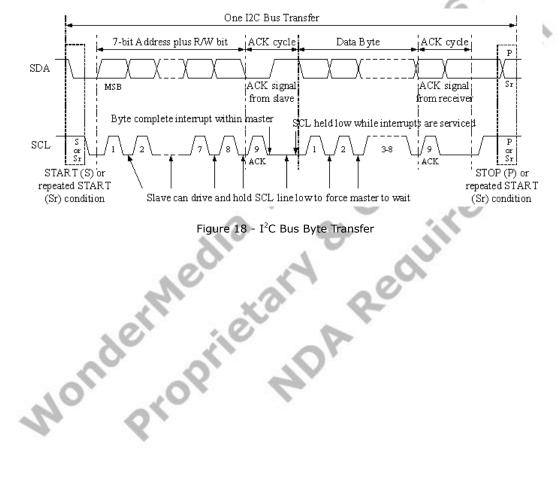

| I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |

| Electrical Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 207                      |

| Storage and Operation Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 207                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

| DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 207                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |

| Voltage Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| Voltage Requirements  Current / Power Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 211                      |

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 211<br>211               |

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 211<br>211               |

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 211<br>211<br>213        |

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 211<br>211<br>213<br>215 |

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 211<br>213<br>215<br>216 |

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| AC Characteristics VGA DAC Interface Timing DRAM Interface Timing Serial Flash Memory Controller Interface Timing Ethernet MAC Interface Timing - MII Mode Ethernet MAC Interface Timing - RevMII Mode KBDC Interface Timing NAND Flash Interface Timing - Command/Address Latch NAND Flash Interface Timing - Data Read NOR/GUP Interface Timing SD/MMC Interface Timing DVO Interface Timing SDTV Digital Video Interface Timing                                                                                                                                                                                                |                          |

| AC Characteristics VGA DAC Interface Timing  DRAM Interface Timing  Serial Flash Memory Controller Interface Timing  Ethernet MAC Interface Timing - MII Mode  Ethernet MAC Interface Timing - RevMII Mode  KBDC Interface Timing  NAND Flash Interface Timing - Command/Address Latch  NAND Flash Interface Timing - Data Read  NOR/GUP Interface Timing  SD/MMC Interface Timing  SD/MMC Interface Timing  SDTV Digital Video Interface Timing  CMOS Sensor Interface Timing                                                                                                                                                    |                          |

| AC Characteristics  VGA DAC Interface Timing  DRAM Interface Timing  Serial Flash Memory Controller Interface Timing.  Ethernet MAC Interface Timing - MII Mode  Ethernet MAC Interface Timing - RevMII Mode.  KBDC Interface Timing  NAND Flash Interface Timing - Command/Address Latch  NAND Flash Interface Timing - Data Read  NOR/GUP Interface Timing  SD/MMC Interface Timing  SD/MMC Interface Timing  SDTV Digital Video Interface Timing  CMOS Sensor Interface Timing  Audio I <sup>2</sup> S Interface Timing                                                                                                        |                          |

| AC Characteristics  VGA DAC Interface Timing  DRAM Interface Timing  Serial Flash Memory Controller Interface Timing.  Ethernet MAC Interface Timing - MII Mode  Ethernet MAC Interface Timing - RevMII Mode.  KBDC Interface Timing  NAND Flash Interface Timing - Command/Address Latch  NAND Flash Interface Timing - Data Read  NOR/GUP Interface Timing  SD/MMC Interface Timing  DVO Interface Timing  SDTV Digital Video Interface Timing  CMOS Sensor Interface Timing  Audio I <sup>2</sup> S Interface Timing  UART Interface Timing                                                                                    |                          |

| AC Characteristics  VGA DAC Interface Timing  DRAM Interface Timing  Serial Flash Memory Controller Interface Timing.  Ethernet MAC Interface Timing - MII Mode.  Ethernet MAC Interface Timing - RevMII Mode.  KBDC Interface Timing  NAND Flash Interface Timing - Command/Address Latch.  NAND Flash Interface Timing - Data Read  NOR/GUP Interface Timing  SD/MMC Interface Timing  SDVO Interface Timing  SDTV Digital Video Interface Timing.  CMOS Sensor Interface Timing  Audio I <sup>2</sup> S Interface Timing  UART Interface Timing  SPI Interface Timing  SPI Interface Timing                                    |                          |

| AC Characteristics  VGA DAC Interface Timing  DRAM Interface Timing  Serial Flash Memory Controller Interface Timing  Ethernet MAC Interface Timing - MII Mode  Ethernet MAC Interface Timing - RevMII Mode  KBDC Interface Timing  NAND Flash Interface Timing - Command/Address Latch  NAND Flash Interface Timing - Data Read  NOR/GUP Interface Timing.  SD/MMC Interface Timing.  DVO Interface Timing.  SDTV Digital Video Interface Timing  CMOS Sensor Interface Timing  Audio I²S Interface Timing  UART Interface Timing  SPI Interface Timing  SPI Interface Timing  I²C Interface Timing.                             |                          |

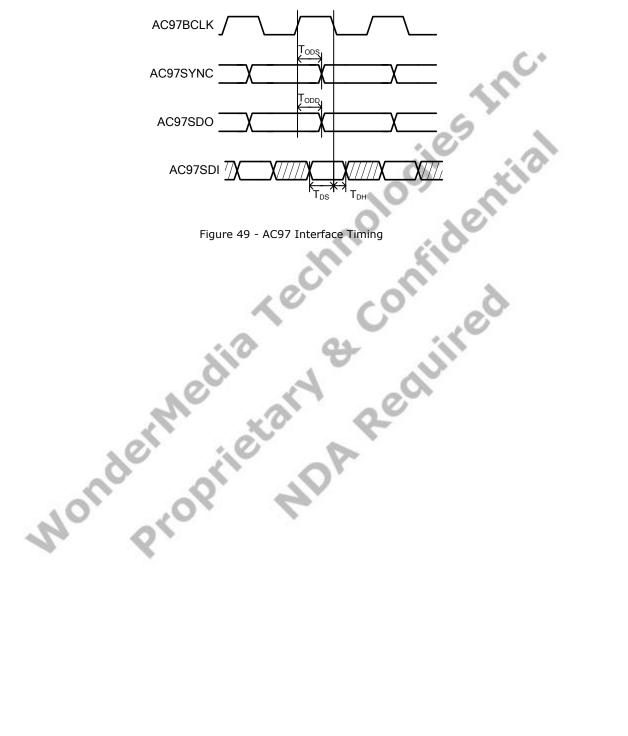

| AC Characteristics VGA DAC Interface Timing DRAM Interface Timing Serial Flash Memory Controller Interface Timing. Ethernet MAC Interface Timing - MII Mode Ethernet MAC Interface Timing - RevMII Mode KBDC Interface Timing NAND Flash Interface Timing - Command/Address Latch NAND Flash Interface Timing - Data Read NOR/GUP Interface Timing SD/MMC Interface Timing SD/MMC Interface Timing DVO Interface Timing SDTV Digital Video Interface Timing. CMOS Sensor Interface Timing. Audio I²S Interface Timing. UART Interface Timing SPI Interface Timing I²C Interface Timing I²C Interface Timing AC97 Interface Timing |                          |

| AC Characteristics  VGA DAC Interface Timing  DRAM Interface Timing  Serial Flash Memory Controller Interface Timing  Ethernet MAC Interface Timing - MII Mode  Ethernet MAC Interface Timing - RevMII Mode  KBDC Interface Timing  NAND Flash Interface Timing - Command/Address Latch  NAND Flash Interface Timing - Data Read  NOR/GUP Interface Timing.  SD/MMC Interface Timing.  DVO Interface Timing.  SDTV Digital Video Interface Timing  CMOS Sensor Interface Timing  Audio I²S Interface Timing  UART Interface Timing  SPI Interface Timing  SPI Interface Timing  I²C Interface Timing.                             |                          |

# List of Figures

| Figure 1 - WM8505 System Block Diagram                                          | 5   |

|---------------------------------------------------------------------------------|-----|

| Figure 2 - WM8505 Software Architecture                                         | 6   |

| Figure 3 - WM8505 Ball Diagram – Left (Top View)                                |     |

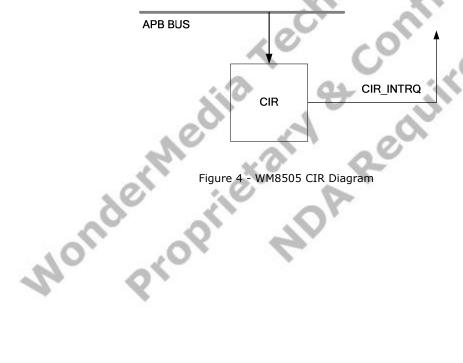

| Figure 4 - WM8505 CIR Diagram                                                   | 146 |

| Figure 5 - WM8505 Power Domains                                                 | 177 |

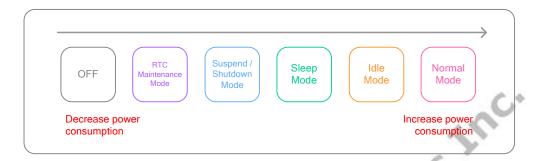

| Figure 6 - Power Modes and Power Consumption                                    |     |

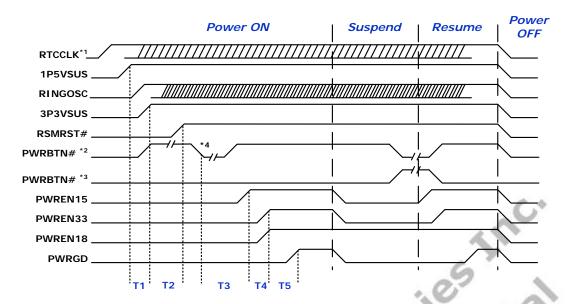

| Figure 7 - Power On Sequence w/ Suspend Power                                   |     |

| Figure 8 - Power On Sequence w/ Non-Suspend Power                               | 182 |

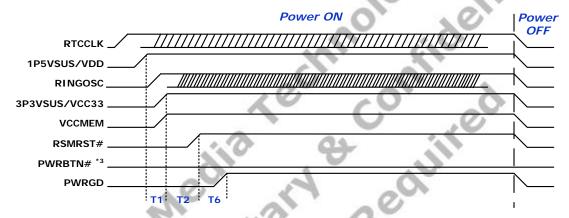

| Figure 9 - 27 MHz Crystal Network                                               |     |

| Figure 10 - Internal Clock Generation of 25 MHz Clock Network                   | 186 |

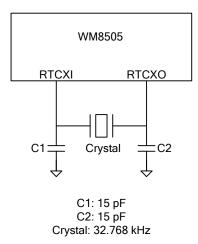

| Figure 11 - RTC Crystal Network                                                 | 187 |

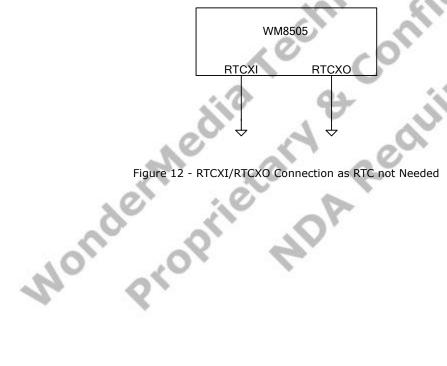

| Figure 12 - RTCXI/RTCXO Connection as RTC not Needed                            | 187 |

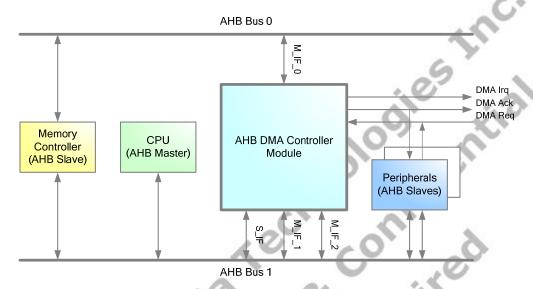

| Figure 13 - AHB DMA Controller in System                                        | 188 |

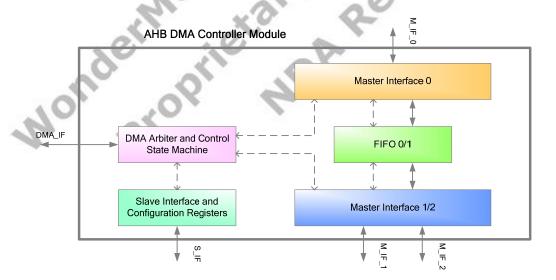

| Figure 14 - AHB DMA Controller Internal Block Diagram                           |     |

| Figure 15 - DMA Rotating Priority Scheme                                        |     |

| Figure 16 - Audio Controller Module Block Diagram                               | 100 |

| Figure 17 - UART Serial Data Transfer Format                                    |     |

| Figure 18 - I <sup>2</sup> C Bus Byte Transfer                                  | 201 |

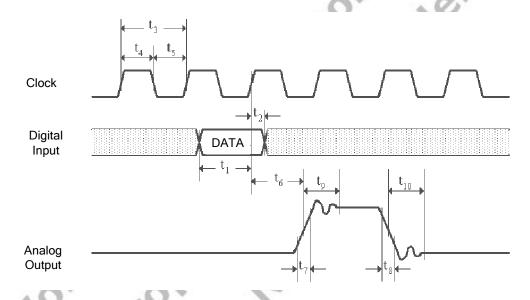

| Figure 19 - DATA Timing Diagram                                                 | 200 |

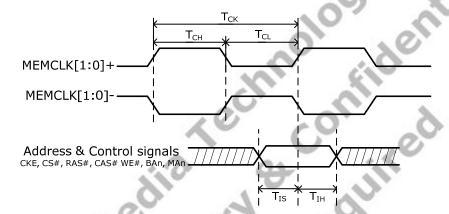

| Figure 20 - Command Timing Dagram                                               | 212 |

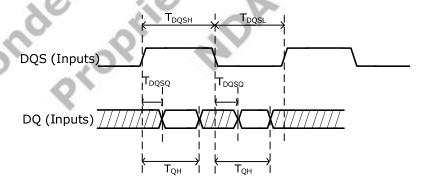

| Figure 21 - DQ/DQS Read Timing Diagram                                          |     |

|                                                                                 |     |

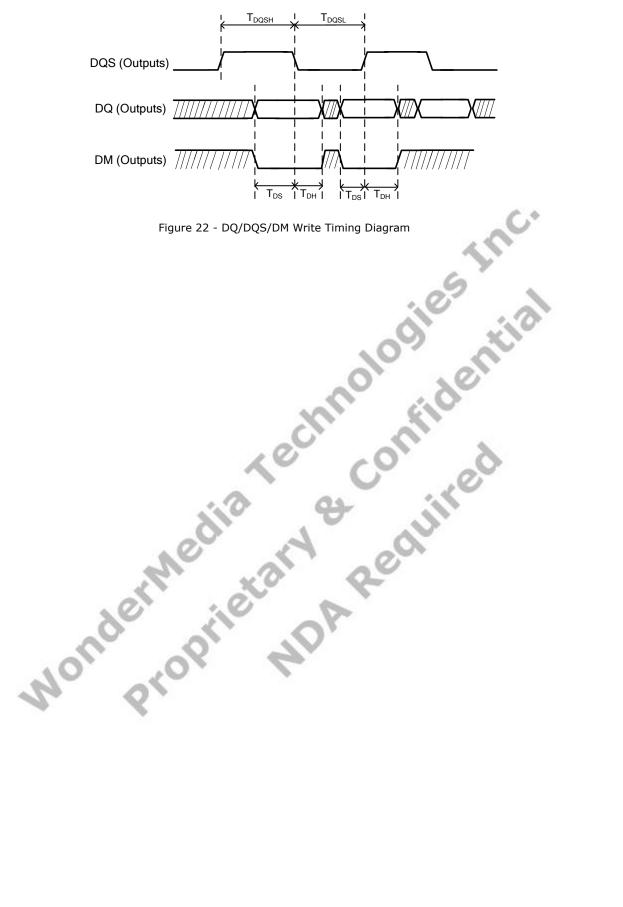

| Figure 22 - DQ/DQS/DM Write Timing Diagram                                      | 214 |

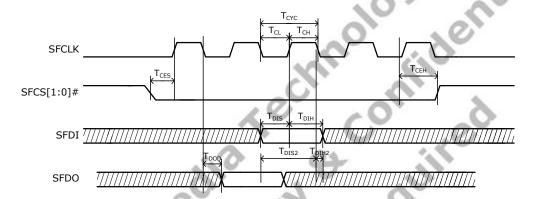

| Figure 23 - Serial Flash Memory Controller Interface Timing                     | 215 |

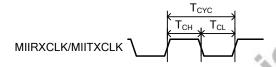

| Figure 24 - Ethernet MAC Interface Timing – Clock                               | 210 |

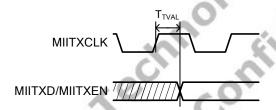

| rigure 25 - Ethernet MAC Interface Timing - Transmit Timing                     | 216 |

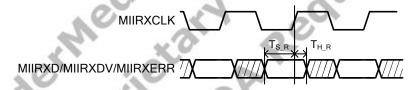

| Figure 26 - Ethernet MAC Interface Timing -Setup & Hold Time                    |     |

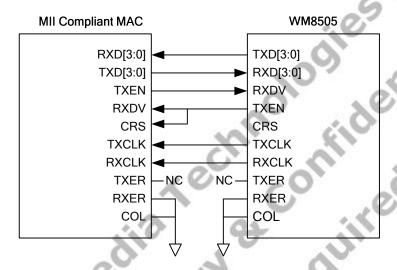

| Figure 27 - RevMII Connection Diagram                                           | 217 |

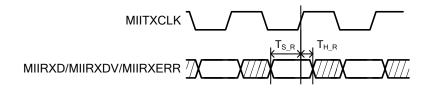

| Figure 28 - Ethernet MAC Interface Timing -Setup & Hold Time                    | 217 |

| Figure 29 - Ethernet MAC Interface Timing -Setup & Hold Time                    | 21/ |

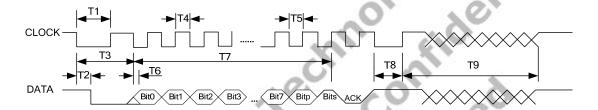

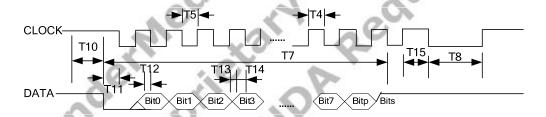

| Figure 30 - KBDC Interface Timing – Sending Data to External Keyboard/mouse     | 218 |

| Figure 31 - KBDC Interface Timing – Reveiving Data from External Keyboard/mouse | 218 |

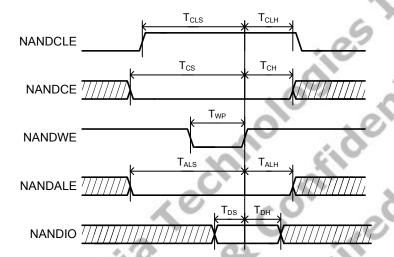

| Figure 32 - NAND Flash Interface Timing - Command Latch                         | 219 |

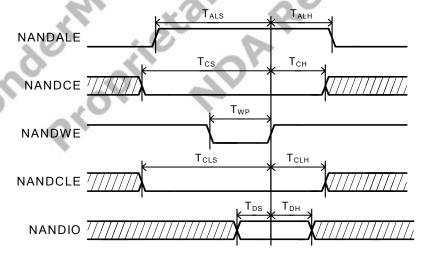

| Figure 33 - NAND Flash Interface Timing - Address Latch                         | 219 |

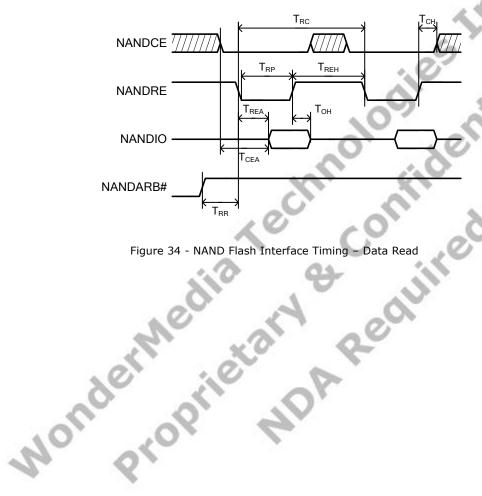

| Figure 34 - NAND Flash Interface Timing – Data Read                             | 220 |

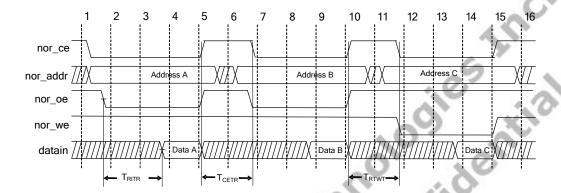

| Figure 35 - Read Timing - Read Initial Cycle Timing in Asynchronous Read        | 221 |

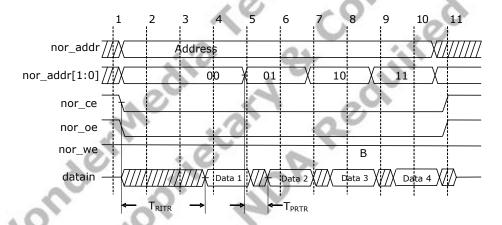

| Figure 36 - Page Mode Read Timing in Asynchronous Mode                          | 221 |

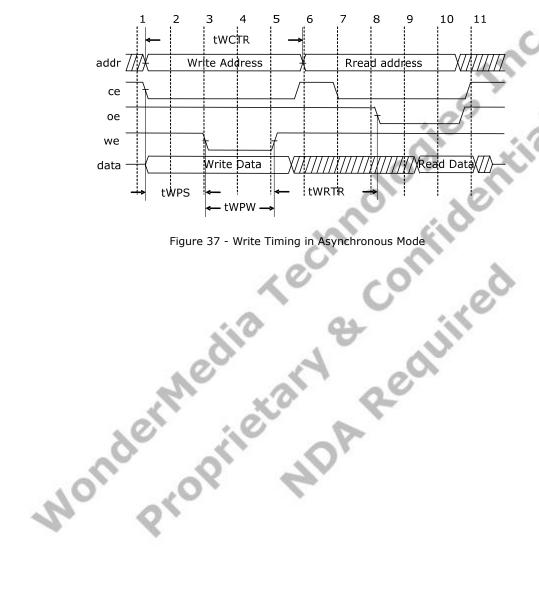

| Figure 37 - Write Timing in Asynchronous Mode                                   | 222 |

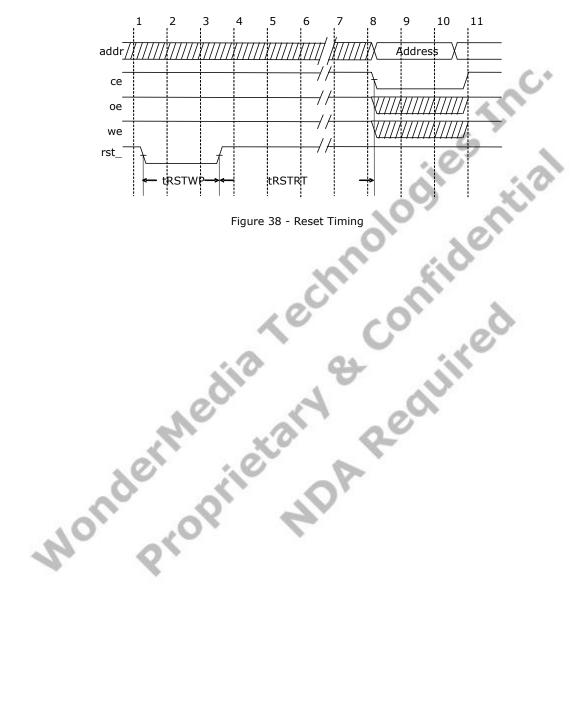

| Figure 38 - Reset Timing                                                        | 223 |

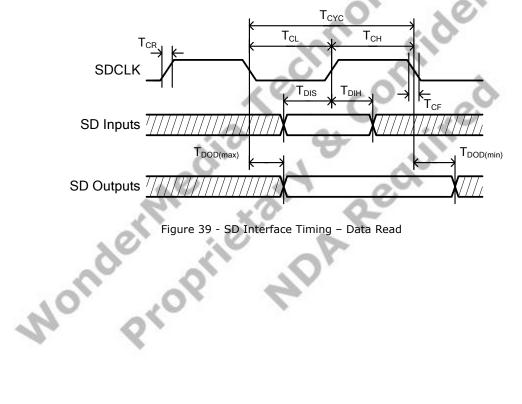

| Figure 39 - SD Interface Timing - Data Read                                     | 224 |

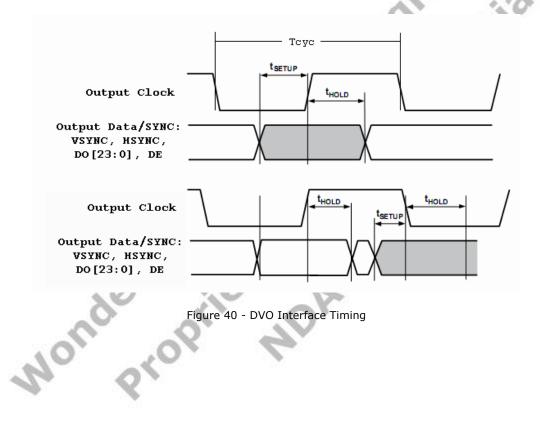

| Figure 40 - DVO Interface Timing                                                | 225 |

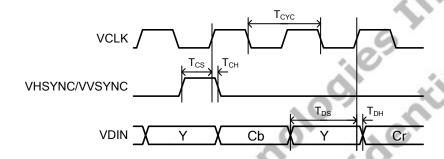

| Figure 41 - CCIR-656/601 Input Pixel Data Timing                                | 226 |

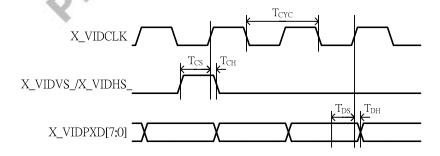

| Figure 42 - CMOS Sensor Input Pixel Data Timing                                 | 226 |

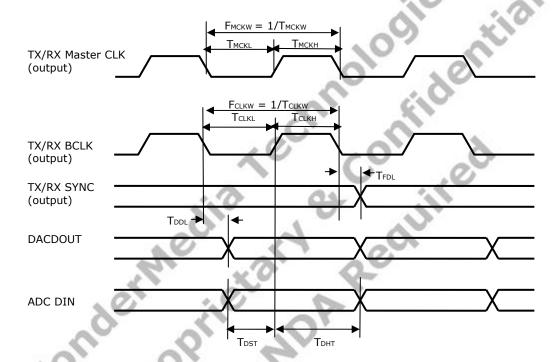

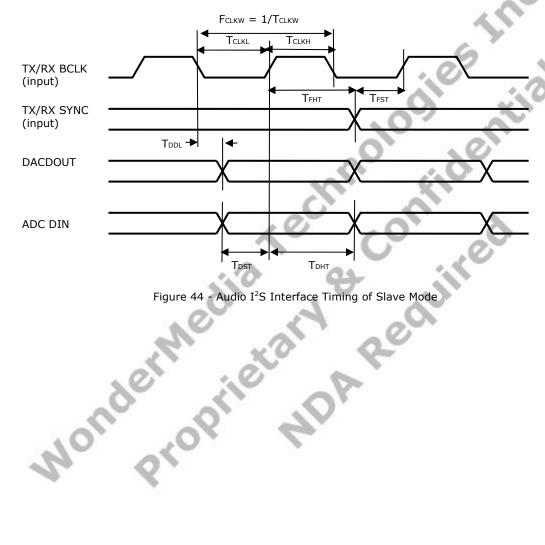

| Figure 43 - Audio I <sup>2</sup> S Interface Timing of Master Mode              | 227 |

| Figure 44 - Audio I <sup>2</sup> S Interface Timing of Slave Mode               |     |

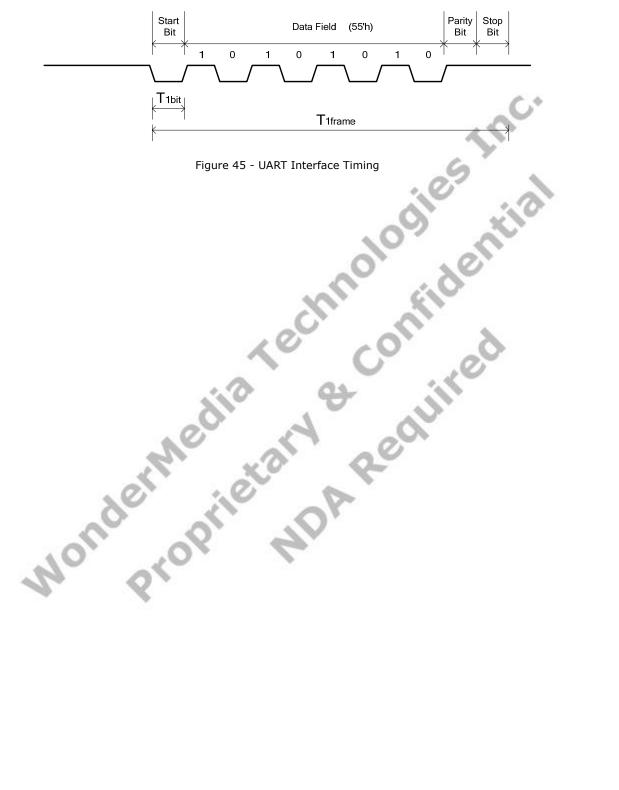

| Figure 45 - UART Interface Timing                                               | 229 |

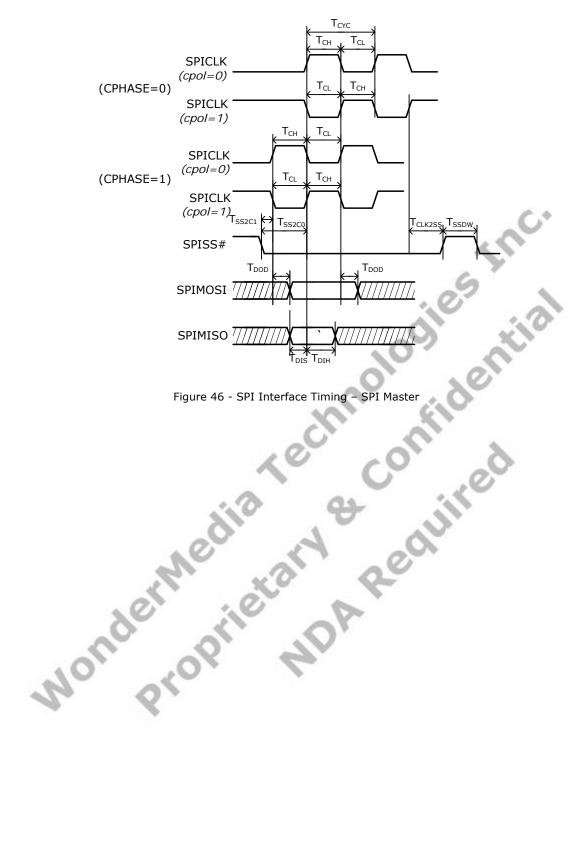

| Figure 46 - SPI Interface Timing – SPI Master                                   | 231 |

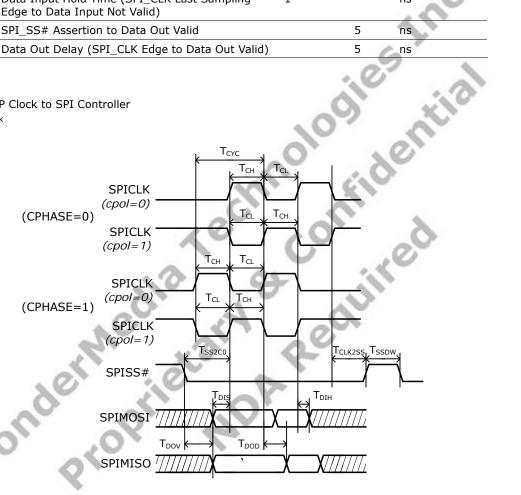

| Figure 47 - SPI Interface Timing - SPI Slave                                    | 232 |

| Figure 48 - I <sup>2</sup> C Interface Timing                                   | 233 |

| Figure 49 - AC97 Interface Timing                                               | 234 |

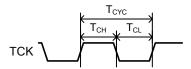

| Figure 50 - ARM JTAG Interface Timing – Test Clock                              | 235 |

| Figure 51 - ARM JTAG Interface Timing – Test Reset                              | 235 |

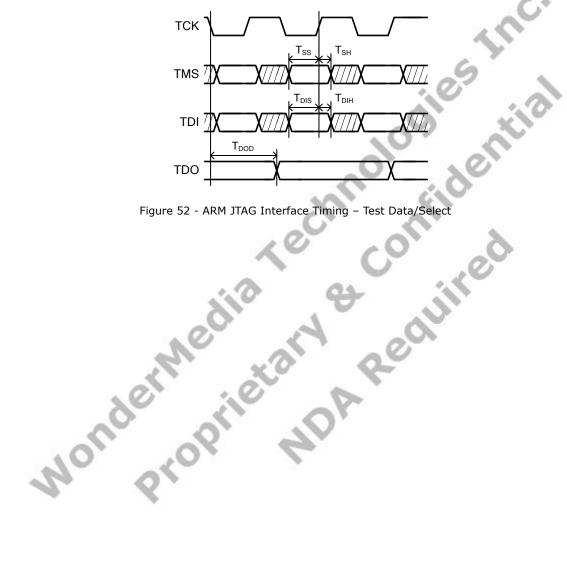

| Figure 52 - ARM JTAG Interface Timing – Test Data/Select                        |     |

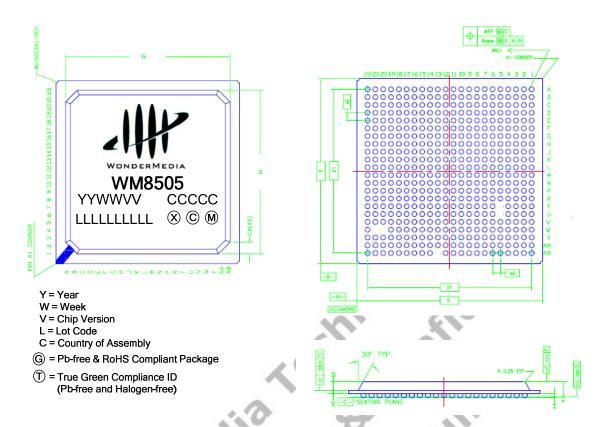

| Figure 53 - WM8505 Mechanical Specification                                     | 237 |

# List of Tables

| Table 1 - WM8505 Ball and Signal List – Sorted by Ball Number                            | 9   |

|------------------------------------------------------------------------------------------|-----|

| Table 2 – WM8505 Ball and Signal List – Sorted by Signal Name                            | 11  |

| Table 3 – WM8505 Power and Ground Ball List                                              |     |

| Table 4 - WM8505 Memory Map                                                              | 26  |

| Table 5 - Transmit FIFO Byte Write Method                                                |     |

| Table 6 - Direct SSN Control                                                             |     |

| Table 7 - PCM Tx FIFO Write Port (PTFIFO) Valid Access                                   |     |

| Table 8 - PCM Tx FIFO Write Port (PTFIFO)                                                |     |

| Table 9 - PCM Rx FIFO Read Port (PRFIFO) Valid Access                                    |     |

| Table 10 - PCM Rx FIFO Read Port (PRFIFO)                                                |     |

| Table 11 - Mic FIFO Read Port (MFIFO) Valid Access                                       |     |

| Table 12 - Mic FIFO Read Port (MFIFO)                                                    |     |

| Table 13 - Data Size of Playback Data Written from MCU or APB Interface for Each Channel |     |

| Table 14 - Data Size of Record Data Read by MCU or APB Interface for Each Channel        |     |

| Table 15 - Typical Timing Values of Initial Power-on Sequence                            |     |

| Table 16 - WM8505 Strapping Options                                                      |     |

| Table 17 - Audio Master Clock Frequency Selection                                        |     |

| Table 19 - Frame Buffer Format for 1 bpp Data                                            | 106 |

| Table 20 - Interrupt Controller 0 Request Sources                                        |     |

| Table 21 - Interrupt Controller 1 Request Sources                                        | 200 |

| Table 22 - UART Baud Rate Examples                                                       |     |

| Table 23 - CCIR-656/601 Input Pixel Data Timing                                          | 226 |

| Table 24 - CMOS Sensor Input Pixel Data Timing                                           |     |

| Table 25 - Audio I <sup>2</sup> S Interface Timing of Master Mode                        |     |

| Table 26 - Audio I <sup>2</sup> S Interface Timing of Slave Mode                         |     |

| Table 27 - SPI Interface Timing - SPI Master, Divisor = 0                                |     |

| Table 28 - SPI Interface Timing – SPI Master, Divisor ≥ 1                                |     |

| Table 29 - SPI Interface Timing – SPI Slave                                              | 232 |

| Table 30 - I <sup>2</sup> C Interface Standard and Fast Mode Timing                      |     |

| Table 31 - I <sup>2</sup> C Interface High Speed Mode Timing                             |     |

| Table 32 - ARM JTAG Interface Timing - Test Clock                                        | 235 |

| Table 33 - ARM JTAG Interface Timing - Test Reset                                        | 235 |

| Table 34 - ARM JTAG Interface Timing - Test Data/Select                                  | 236 |

| Monder Merietain Reco                                                                    |     |

|                                                                                          |     |

# **Product Features**

## WM8505 Application Processor

Scalable Powerful RISC Core Built-in Versatile Peripherals Performance-enhanced JPEG Decoder Simplified Design/Development with Low System BOM

#### 300 MHz ARM926F LS RISC Processor

- ARM (Advanced RISC Microelectronics) 926EJ-S RISC Processor with MMU, 16k Bytes Instruction Cache and 16k Bytes Data Cache

- Maximum Operating Frequency of 300 MHz @ 1.5V Core Power Voltage OUTEDANTIE

- 32/16-bit RISC Architecture (ARMv5TEJ)

- 32-bit ARM Instruction Set and 16-bit Thumb Instruction Set

- DSP Instruction Extensions and Single Cycle MAC

- ARM Jazelle® Technology for Java® Acceleration

# **DDR2 SDRAM Memory Controller**

- Supports DDR2 SDRAM Controllers, up to DDR2-667

- Programmable Memory Timing

- Supports 16-bit Memory Interface

- Supports up to 512 MB

## JPEG/Motion JPEG Decoder

JPEG Baseline Profile Decoding Capability

## Video Post-Processing Unit

- Built-in 2D Graphic Engine (65536/16.7M colors; 16 bpp/32 bpp) for Graphics-base Application

- Support 1 Video and 2 Graphic Planes with Variety of Mixing Effects

- 2D GE Supports Alpha Bitblt, ROP3, ROP4, Line Draw, and Rotate/Mirror Operations

- Video Overlay Engine for Video, and Graphic Planes

- Video H/V Scalar Capability (Arbitrary Scaling Limitation 0.125 ~ 16.0 with Bi-Linear Interpolation)

## Video Interface

- Supports 24-bit Color VGA Output Mode for PC Monitor up to 1024x600 @ 60 Hz Refresh Rate

- Supports 24-bit Color DVO Digital Video Output for External DVI/LVDS/HDMI Video Transmitter up to 1024x600 @ 60 Hz Refresh Rate

- Supports Direct CCIR-656/601 Digital Video Input from External Video Decoder

- Supports CMOS Sensor Digital Input from External CMOS Sensor Module

## Audio Interface

- On-chip Audio Frequency Synthesizer to Support Sampling Rate up to 192 KHz

- I2S Audio Interface with 2-ch input and output

- AC97 Audio Interface

## Flash Memory Support

- Serial Flash Memory Controller

- Supports Serial Flash (SPI) Memory Modules

- Supports Two Chip Selects, up to 16 MB each

- Strapping Option to Select whether NOR or Serial Flash Memory is used as Boot Device

S. P. Hind

## NAND Flash Interface

- Supports 32 Mb 32 Gb Flash

- Supports up to 8-pcs Flash Chips

- Allows Different Memory Type for Each Channel

- Supports Both 8-bit and 16-bit Flash

- Built-in Hardware 4-bit/8-bit ECC Correction for MLC Device and 1-bit ECC Correction for SLC Device (512-bytes ECC Calculation)

- Configurable Timing Parameters

- Supports Multi-Sector Read Operation

- Supports High-Speed Programming (multi-block erase and multi-block program)

## • Secure Digital (SD) / SDIO / Multimedia Card (MMC) Interfaces

- Supports One SD/SDIO/MMC Interface

- SD Memory Card Spec. 2.0 / SDIO Spec. 1.0 / MMC Spec. 4.2 Compatible

- All SD Bus Modes Supported, Including SPI, 4-bit and 1-bit SD

- SD and MMC Support Different Clock Rate from 390 kHz to 52 MHz

- Supports CE-ATA Interface (compatible with MMC Version 4.2)

- Supports High Capacity Cards

## USB 2.0 Host / Device Controller

- Supports 2 USB Host Ports and One Device Port

- USB2.0/EHCI 1.0/UHCI1.1d Specification Compliant

- Integrated Root Hub with 2 Ports

- Support High/Full/Low Speed Devices

- USB2.0 UTMI Compliant

## • 10/100 Ethernet MAC

- 802.3x Full Duplex Flow Control and Half Duplex Force Jam Capable

- MII Interface for External Ethernet PHY Support

- RevMII Interface for Switch Connectivity (Reverse MII)

## Serial Peripheral Interface (SPI) Ports

- Three SPI Channels

- Industry Standard Serial Peripheral Interface

- Master and Slave SPI Modes Supported

- All Channels Support Master Modes and Slave Mode 0 and 2

- Four Signal Interfaces for each Port Clock, Select, Transmit Data and Receive Data

- Full Duplex Synchronous Serial Data Transfer

- Programmable Clock Phase and Polarity

- Programmable Asynchronous Transmission Speed up to 100 MHz

# UART / IrDA Communication Ports

- Up to Six Half UARTs or Four Full UARTs Supported. One UART Port with Additional Support for IrDA Version 1.0 Short Range Infrared Communication

- 16C550 Compliant UARTs with Baud Rate Support from 900 to 921.6k bps (2.4k to 115.2k bps for IrDA)

- DMA Data Transfer Capability Using the on-chip System DMA Controller

- RTS and CTS Modem Handshake Control Signals for Each UART when IrDA is not Used

- Supports Bluetooth UART HCI Communication Break Signal Generation

# I<sup>2</sup>C Serial Port

- Two I<sup>2</sup>C Ports Supported

- 100k bps Standard Mode plus 400k bps Fast Mode

- 7-bit Address

- Signal-master (Multi-master not Supported)

- Supports Slave Mode in one of the I<sup>2</sup>C Ports

- Software Programmable Clock Frequency and Acknowledge Bit

- Interrupt Driven Data Transfer

## Hardware Security Acceleration Engine

- Supports AES-128 Encryption / Decryption with ECB/CBC/CTR/OFB Mode

- Supports SHA-1 (Secure Hash Algorithm) Hash Function

- Supports RC4 Decryption

## · Keypad Interface

Supports up to 8x8 Key Matrix if CCIR601/656 Digital Video Input Interface and One of the I<sup>2</sup>C Serial Ports (I<sup>2</sup>C1x) are not Used

## PS/2 Keyboard Mouse Interface

- PS/2 & AT Keyboard and Mouse Supported

- Intel 8042 Controller Compatible

- Wakeup from Suspend Supported

- Support Keyboard/Mouse Interface swapping

## Built-in CIR Modulation Detection and Decode

- Supports NEC, Sony, Matsushita, and JVC Code Formats

## Pulse Width Modulation System Timer

- 2 PWM Timers that may be Used as either PWM Timers or Simple System Timers

- 2 PWM Timer Outputs to External Logic

#### General Purpose I/O

- 8 Dedicated General Purpose I/Os with Level/Edge Sensitive Interrupt Requests

- Other Multiplexed GPIO Signals Allow One or More Peripherals to be Disabled for Multiplexed GPIO Signal Sections

# System Interrupt Controller

- Support for up to 128 Interrupt Sources

- Generates Interrupt and Fast-Interrupt to ARM

- Interrupt Status Registers for Every Interrupt Output

- Fixed and Rotating Priority Schemes

- 16 External Interrupt Sources through GPIO Pins that are Edge or Level Sensitive

## System DMA Controller

- 16 Channels

- Supports Scatter-Gather DMA Operation

- Memory-to-Peripheral Transfers, Peripheral-to-Memory Transfers and Memory-to-Memory Transfers Supported

- 1-, 4-, and 8- Transfer Burst Sizes and 8 / 16 / 32-Bit Data Widths

- Supports Dual DMA Buffers in Ping-Pong Fashion

# Real Time Clock

- With on-chip Low Power 32.768 kHz Oscillator Requiring only a Crystal

- Supports Time, Date and Day-of-the-week

- Provides Time and Date in 24-hour or 12-hour Format with an AM/PM Flag

- Encodes the Seconds, Minutes, Hours, Days, Months and Years in BCD Format

- Calendar Function with Correction for Leap Year

- Time Calibration (Providing a Time Correction Mechanism)

- Programmable Alarm with Interrupt Request Generation

- Second / Minute Updating Interrupt Request Generation

## Reset and Power Management

- Supports Four Operating Modes: Normal, Idle, Sleep and Suspend

- Gate-off Function of Peripheral Clocks to Put Unused Peripherals in Low Power Mode

## PLLs and Clock Control

- Built-in PLLs to Provide Various Clock Frequencies

- Internal Oscillator Only One 27 MHz Crystal is Needed Externally

## Operating System Timer

- Generates Periodic Interrupts for System Purposes

- Generates Watchdog Reset

## • JTAG Debugging Interface

- In Compliance with IEEE 1149.1

- All Internal Memory with BIST

## Operating Temperature

Commercial Grade: Ranges from 0°C to 70°C

## 479-ball PBGA Package (19 x 19 mm with 0.8 mm ball pitch)

## **Operating Systems**

- Embedded Linux

- Windows CE

# Supporting Software Package (based on selected OS)

- Device Drivers for Internal Peripherals

- Supporting Binary Library, i.e. Linux Loadable Modules

- Porting Guide

- Sample Applications for Chip Validation, System H/W Evaluation, and Reference Design Wondermedia Technologies Inc.

Wondermedia Technologies Inc.

ADA Required

- Application Shell

- Media Player

# WM8505 System Overview

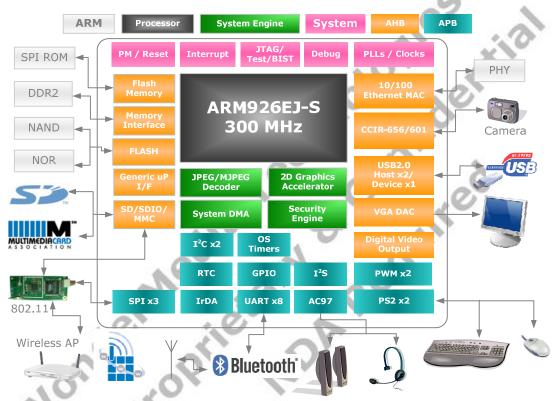

The WM8505 Application Processor is the SoC solution with superior networks and display capabilities that specially tailored for cost-effective embedded multimedia devices. The WM8505 supports display resolution up to 1024x600 and 10/100 Ethernet MAC. The WM8505 is a low power consumption SoC solution that demands 1.8V for DDR2 SDRAM, and 3.3 V for other interfaces as operating power. The WM8505 integrates multimedia features and functionalities, e.g. decoding popular audio/video streams, 2D graphics display, and peripheral I/Os that are aiming to meet upcoming market demands as well as reduce customer's total BOM cost. The WM8505 is designed to deliver the state-of-the-art performance for applications such as Networked Projector, Digital Signage, and Thin-Client Terminal.

The WM8505 Application Processor integrates all popular peripherals in an efficiently architected RISC (reduced instruction set computer) platform. Figure 1 illustrates the system block diagram of WonderMedia's WM8505 Application Processor.

Figure 1 - WM8505 System Block Diagram

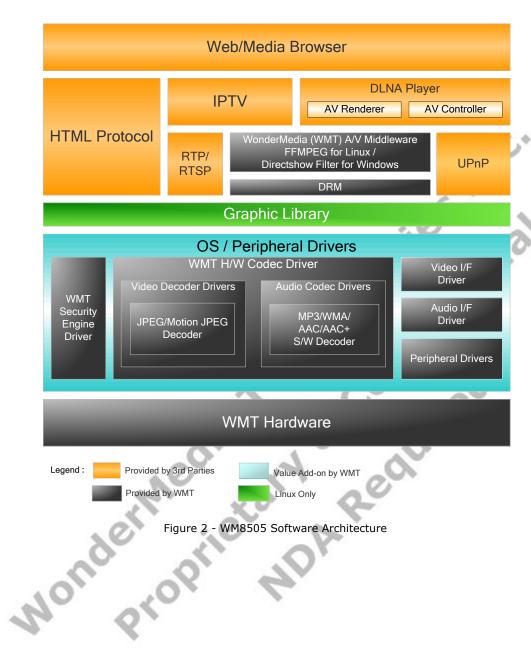

Figure 2 illustrates the software architecture of the WM8505 Application Processor. The WM8505 supports Linux and Windows CE for embedded systems. WonderMedia provides the software package that includes device drivers for multimedia, peripheral, and security-related devices as well as multimedia player with high audio, video, and image quality. The software architecture of WM8505 can easily collaborate with the 3<sup>rd</sup> party software packages to provide versatile applications.

# Ballout: 479-ball PBGA Package (19 x 19 mm with 0.8 mm ball pitch)

|    | 1            | 2                  | 3                   | 4        | 5                | 6                   | 7                   | 8                   | 9                   | 10                  | 11                  |

|----|--------------|--------------------|---------------------|----------|------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| А  | NC           | MIIOMDIO           | MIIOMDC             | MII0RXD3 | MII0RXD0         | MIIOTXC             | MII0TXD1            | PWREN33             | PWREN18             | PWREN15             | PWRBTN#             |

| В  | NC           | NC                 | MIIORXDV            | GND      | MIIORXC/G<br>RXC | GND                 | MII0TXD0            | MIIOPHYPD<br>#      | WAKEUP3             | RSMRST#             | MSDT                |

| С  | NC           | GND                | NC                  | MIIORXER | MII0RXD1         | MII0TXD3            | MII0COL             | MIIOTXEN            | WAKEUP0             | WAKEUP2             | KBDT                |

| D  | NC           | NC                 | NC                  | NC       | MII0RXD2         | MII0TXD2            | MIIOCRS             | PHY25MHZ            | MIIOPHYRS<br>T#     | WAKEUP1/<br>USBATTA | VSUS33              |

| E  | NC           | NC                 | NC                  | GND      | NC               | GND                 | VSUS33              | VSUS33              | GND                 | VSUS15              | VSUS33              |

| F  | NC           | GND                | NC                  | NC       | NC               | VSUS33              | VCC33               | VCC33               | VCC33               | VCC33               | VCC33               |

| G  | NC           | NC                 | NC                  | NC       | MEMCOMP          | VCCMEM              | VDD                 | VDD                 | VDD                 | VDD                 | VDD                 |

| Н  | MEMA01       | MEMA02             | NC                  | GND      | MEMCS0#          | VCCMEM              | VDD                 | GND                 | GND                 | GND                 | GND                 |

| J  | MEMA07       | MEMA04             | MEMA00              | MEMA03   | MEMVREF0         | VCCMEM              | VDD                 | GND                 | GND                 | GND                 | GND                 |

| К  | MEMA06       | GND                | MEMRAS#             | MEMCAS#  | MEMWE#           | VCCMEM              | VDD                 | GND                 | GND                 | GND                 | GND                 |

| L  | MEMA05       | MEMA08             | MEMBA0              | GND      | MEMODT           | VCCMEM              | VDD                 | GND                 | GND                 | GND                 | GND                 |

| М  | MEMA10       | MEMA09             | MEMA11              | MEMA12   | MEMBA1           | VCCMEM              | VDD                 | GND                 | GND                 | GND                 | GND                 |

| N  | MEMD08       | GND                | MEMD13              | MEMA13   | MEMCKE           | VCCMEM              | VDD                 | GND                 | GND                 | GND                 | GND                 |

| Р  | MEMCLK-      | MEMCLK+            | MEMD14              | GND      | MEMBA2           | VCCMEM              | VDD                 | GND                 | GND                 | GND                 | GND                 |

| R  | MEMDQM1<br># | MEMDQS1<br>+       | MEMDQS1-            | MEMD10   | MEMVREF1         | VCCMEM              | VDD                 | GND                 | GND                 | GND                 | GND                 |

| Т  | MEMD15       | GND                | MEMD11              | MEMD12   | $\times$         | NORA10              | VDD                 | VDD                 | VDD                 | VDD                 | VDD                 |

| U  | MEMD09       | MEMD03             | MEMD01              | GND      | $\times$         | NORA11              | NORBAA#             | VCC33               | VCC33               | VCC33               | VCC33               |

| v  | MEMD07       | MEMDQS0<br>+       | MEMDQS0-            | MEMD05   | NORCLK           | NORA06/N<br>ANDCE6# | NORA22              |                     | NORA08/N<br>ANDRB0# | NORD09/N<br>ANDIO09 | NOROE#/N<br>ANDRE#  |

| w  | MEMDQM0<br># | GND                | MEMD02              | NORCE2#  | NORA14           | NORA13              | NORA04/N<br>ANDCE4# | NORA03/N<br>ANDCE3# | NORADV#             | NORRST#/<br>NANDALE | NORWE#/N<br>ANDWE#  |

| Y  | MEMD00       | MEMD04             | NORCE3#             | NORA12   | NORA20           | NORA17              |                     | NORD14/N<br>ANDIO14 | GND                 |                     | NORCE0#/<br>NANDCLE |

| AA | MEMD06       | NORA24/G<br>UPBE1# | NORA15              | NORA21   | NORA18           |                     |                     | NORD12/N<br>ANDIO12 |                     |                     |                     |

| АВ | NORCE1#      |                    | NORA09/N<br>ANDRB1# | NORA19   | NORA16           |                     |                     | NORD13/N<br>ANDIO13 |                     |                     |                     |

|    | 1            | 2                  | 3                   | 4        | 5                | 6                   | 7                   | 8                   | 9                   | 10                  | 11                  |

Figure 3 - WM8505 Ball Diagram - Left (Top View)

| 12                        | 13                  | 14       | 15               | 16       | 17                        | 18                      | 19                       | 20                      | 21                       | 22                       |    |

|---------------------------|---------------------|----------|------------------|----------|---------------------------|-------------------------|--------------------------|-------------------------|--------------------------|--------------------------|----|

| PWRGD                     | USBP2-              | GND      | RTCXI            | VBAT     | MMCDATA4                  | SDCLK                   | SDDATA0                  | VDOUT23                 | VDOUT20                  | VDOUT19                  | Α  |

| MSCK                      | USBP2+              | USBP1-   | RTCXO            | SDDATA2  | SDCMD                     | MMCDATA6                | GND                      | VDOUT22                 | GND                      | VDOUT18                  | В  |

| KBCK                      | GND                 | USBP1+   | USBREXT          | SDDATA3  | MMCDATA5                  | MMCDATA7                | VDOUT21                  | VDOUT17                 | VDOUT16                  | VDOUT15                  | С  |

| SUSGPIO                   | USBOC1#             | USBP0+   | VCCA33US<br>BPLL | SDDATA1  | VDOUT14                   | GND                     | VDOUT13                  | GND                     | VDOUT12                  | VDOUT11                  | D  |

| VSUS33                    | USBOC0#             | USBP0-   | VCCA15US<br>BPLL | SDWP     | VDOUT10                   | VDOUT09                 | VDCLK                    | VDOUT08                 | VDOUT07                  | VDOUT06                  | E  |

| VCC33USB                  | VCC33USB            | VCC33USB | VCC33            | VDOUT03  | GND                       | SDCDT                   | GND                      | VDOUT05                 | GND                      | VDOUT04                  | 5  |

| VDD                       | VDD                 | VDD      | VDD              | VCC33    | VDOUT00                   | VDHSYNC                 | VDDEN                    | VDVSYNC                 | VDOUT02                  | VDOUT01                  | G  |

| GND                       | GND                 | GND      | GND              | VDD      | VCC33                     | KPADROW<br>5            | VCCA33PL<br>LAB          | VGAHSYNC                | VGAVSYNC                 | GND                      | Н  |

| GND                       | GND                 | GND      | GND              | VDD      | VCC33                     | CLKTST/<br>KPADROW<br>3 | VCCA33PL<br>LCD          | VGAREXT                 | VGAG                     | VGAR                     | J  |

| GND                       | GND                 | GND      | GND              | VDD      | VCC33                     | GNDAPLL1                | 24MHZXI                  | GND                     | VCCA33DA<br>C            | VGAB                     | K  |